#### PhD Thesis

## Secure Real-Time Transmitter for Continuous Variable Quantum Key Distribution

Department of Physics

Technical University of Denmark

Dino Solar Nikolic

Supervisor: Professor Ulrik Lund Andersen Co-supervisor: Assistant Professor Tobias Gehring

December 2019

## Acknowledgments

This work would not be possible without many people who supported me in various ways for the past three years. It is owed to Ulrik L. Andersen that I had a chance to work in his group in the exciting field of quantum cryptography.

My second supervisor Tobias Gehring is a person with whom I interacted the most. His invaluable knowledge on both quantum optics and engineering was critical for the success of this work.

Experimental quantum cryptography is a field that requires dedicated and coordinated work of a team of people who are focused on different parts of the system. Nitin Jain and Hou-Man Chin did an impressive job on the quantum key distribution optical setup and the receiver. Quantum random number generators were the focus of research of my fellow PhD student Arne Kordts, with whom I had fruitful discussions. Hossein Mani tackled the challenge of efficient error correction codes in continuous variable quantum key distribution. Ruben Grigoryan helped me in the beginning of my studies with his knowledge in electronics. I am greatful that the work of these people is implanted in this thesis.

Special credits go to our collaborator Cosmo Lupo from the University of Sheffield, who significantly contributed to my work with his knowledge of quantum information theory. I am especially thankful for his input for the topics of security of the randomness extraction and Gaussian sampling.

Besides Nitin, Hou-Man, Hossein and Tobias, I thank Haitham El-Ella for reviewing parts of my thesis.

I had a pleasure of spending a few weeks in Cambridge at Toshiba Research Europe thanks to Andrew Shields, Davide Marangon and Zhiliang Yuan.

I thank Alberto Nannarelli from DTU Compute for discussions in the field of FPGA technology.

Tine Hougaard Kitmøller is a person who made sure everything ran smoothly in our group.

Besides all the people who directly contributed to my work, I was lucky to have many friends, both in and out of DTU, who brought happiness to my life and gave me energy to pursue my dreams.

I dedicate this thesis to my parents who supported me unconditionally through my whole life.

## Abstract

Quantum key distribution (QKD) is a cryptographic technique which utilizes quantum phenomena, such as superposition and entanglement, to enable the sharing of a secret random key for encrypted communication. Continuous variable QKD (CV-QKD) offers a practical way for performing a secure key exchange by means of broadband modulation of laser light, where the information is encoded in the light field quadratures.

We focus on building a real-time high-rate CV-QKD transmitter using flexible field programmable gate array (FPGA) chip technology. Composable security for CV-QKD has been proven only for Gaussian modulated quantum states. We implement a high-rate Gaussian sampler using cumulative distribution table (CDT) method. Important security parameters are calculated and the algorithms are realized with respect to maintaining the overall security of the CV-QKD system. Furthermore, digital signal processing (DSP) blocks are implemented in order to support fast (50 MBd/s) exchange of quantum states.

A necessary resource in any QKD protocol is a supply of uniformly distributed random numbers. Such a resource is particularly facilitated by quantum processes, which can be used to generate provably secure random numbers. We employ a high-rate vacuum fluctuation-based quantum random number generator (QRNG) with 8 Gb/s random number output. Our standalone QRNG system includes a real-time entropy testing based on monitoring the power spectral density according to a rigorous security model, instead of using common statistical tests that do not prove security. We address the issue of traditionally slow post-processing with a fast randomness extraction method based on Toeplitz hashing. To our knowledge, this is currently the fastest real-time QRNG implementation. A consequence of this is the fastest implementation of the Gaussian sampler used in CV-QKD. The thesis concludes with the evaluation of the transmitter as a part of our CV-QKD setup. It demonstrates for the first time an all-in-one implementation of transmitter functions for high-rate CV-QKD links. We recognize the potential for wide adoption of CV-QKD in near-future secure communication networks.

**Keywords** Quantum cryptography, CV-QKD, QRNG, FPGA, Gaussian modulation, Toeplitz hashing, Entropy testing

### Resumé

Kvantenøglefordeling (QKD) er en teknik hvor en delt, hemmelig tilfældighed bliver skabt ved brug af kvantefænomener som superpositioner eller sammenfiltring. I særdeleshed tilbyder kvantenøglefordeling med kontinuerte variable (CV-QKD) en praktisk metode til at udveksle en hemmelig nøgle ved at gøre brug af bredbåndet modulation af laser lys, hvor informationen bliver indkodet i lysfeltets kvadraturer.

Vi fokuserer på at bygge en realtid, højrate CV-QKD udsender ved at bruge fleksible felt-programmerbare-port-tabel-chip (FPGA) teknologi. Kombinerbar sikkerhed for CV-QKD er blevet bevist for kun Gaussisk modulerede kvantetilstande. Vi implementerer en højrate Gaussisk sampler ved at gøre brug af den kumulative-fordelings-tabel-metode (CDT). Vigtige sikkerhedsparametre bliver udregnet, og algoritmerne bliver realiseret i forhold til at bevare den overordnede sikkerhed CV-QKD-systemet. Ydermere, bliver digital-signal-behandlings-blokke (DSP) implementeret for at undersøtte hurtig (50 MBd/s) fordeling af kvantetilstande.

En nødvendig ressource i enhver QKD protokol er jævnt fordelte tilfældige tal i særdeleshed beviseligt sikre tilfældige tal genereret af kvanteprocessor. Vi anvender en højrate vakuum fluktuations-baseret QRNG der kan generere tilfældige tal med 8 Gb/s. Vores alene-stående QRNG system inkluderer realtids entropi testning baseret på effekt-spektraltæthedsovervågning ifølge en stringent sikkerhedsmodel i stedet for at benytte almindelige (men ikke informations-teoretisk-sikre) statistiske test. Indtil videre er en flaskehals i tilfældighedsgenereringen efterbehandlingen. Vi adresserer dette problem med en hurtig tilfældigheds-udtræknings-metode baseret på Toeplitz hashing. Efter vores bedste overbevisning, er dette på nuværende tidspunkt den hurtigste realtids QRNG implementering. En konsekvens af dette er den hurtigste implementering af den Gaussiske sampler brugt i QKD.

Denne afhandling afsluttes ved at evaluere udsenderen som en del af vores CV-QKD setup. Den demonstrerer brugbarheden af FPGA-baseret teknologi inden for kvantekryptografi. Vi anerkender potentialet for bred adoption af CV-QKD in nærfremtids sikker-kommunikationsnetværk.

## Contents

| 1 | Intr | roduction                                                      | 1         |

|---|------|----------------------------------------------------------------|-----------|

| 2 | Gaı  | ssian quantum optics and information theory                    | 5         |

|   | 2.1  | Introduction to Gaussian quantum optics                        | 5         |

|   |      | 2.1.1 Quantization of the electromagnetic field and Fock space | 5         |

|   |      | 2.1.2 Phase space representation                               | 8         |

|   |      | 2.1.3 Gaussian states                                          | 9         |

|   | 2.2  | Classical information theory                                   | 11        |

|   | 2.3  | Quantum information theory                                     | 13        |

| 3 | Intr | roduction to continuous variable quantum key distribu-         |           |

|   | tion |                                                                | <b>15</b> |

|   | 3.1  | Security of CV-QKD                                             | 15        |

|   | 3.2  | Building blocks in CV-QKD experiments                          | 18        |

|   |      | 3.2.1 Lasers                                                   | 19        |

|   |      | 3.2.2 Beamsplitters and couplers                               | 19        |

|   |      | 3.2.3 Modulators                                               | 20        |

|   |      | 3.2.4 Automatic bias controller                                | 24        |

|   |      | 3.2.5 Homodyne detection                                       | 24        |

|   |      | 3.2.6 FPGA chips                                               | 29        |

|   | 3.3  | CV-QKD protocols                                               | 36        |

|   | 3.4  | CV-QKD setup                                                   | 38        |

|   | 3.5  | Noise sources in CV-QKD                                        | 39        |

| 4 | Qua  | antum random number generation                                 | <b>43</b> |

|   | 4.1  | The science of randomness generation                           | 43        |

|   | 4.2  | Vacuum fluctuation-based QRNG                                  | 48        |

|   | 4.3  | Theory of randomness extraction                                | 53        |

|   |      | 4.3.1 Universal hashing                                        | 53        |

|   |      | 4.3.2 Almost universal hashing                                 | 56        |

|   |      | 4.3.3 Leftover hash lemma and strong randomness extractors     | 56        |

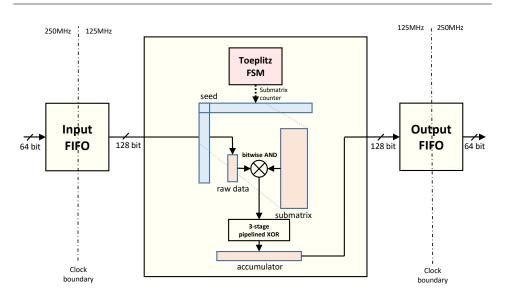

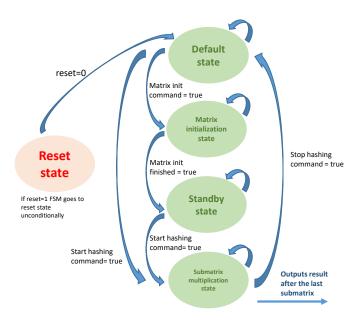

|   | 4.4  | FPGA implementation of the randomness extractor                | 60        |

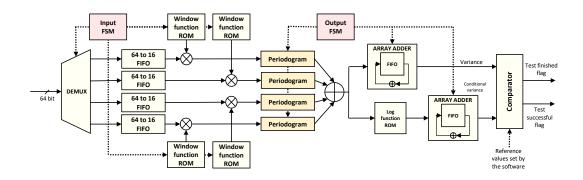

|   | 4.5  | FPGA implementation of the online entropy test                 | 66        |

|   |      |                                                                |           |

#### CONTENTS

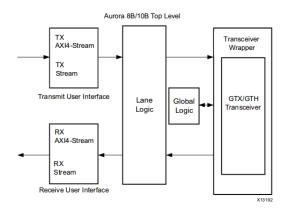

|              | 4.6                                                       | Aurora protocol with SATA interface                                                                                      |     |  |  |

|--------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|--|--|

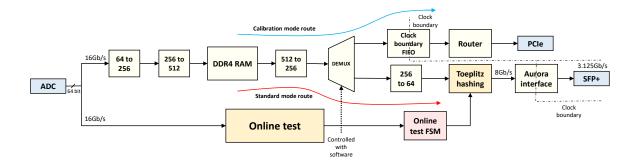

|              | 4.7                                                       | Standalone QRNG: architecture and performance                                                                            | 70  |  |  |

| 5            | Real-time transmitter for continuous variable quantum key |                                                                                                                          |     |  |  |

|              | $\operatorname{dist}$                                     | ribution                                                                                                                 | 77  |  |  |

|              | 5.1                                                       | QKD transmitter architecture                                                                                             | 77  |  |  |

|              | 5.2                                                       | Security of quantum key distribution with realistic Gaussian                                                             |     |  |  |

|              |                                                           | source                                                                                                                   | 78  |  |  |

|              | 5.3                                                       | Generating discrete Gaussian random numbers                                                                              | 83  |  |  |

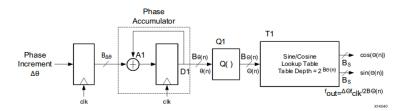

|              | 5.4                                                       | CDT algorithm for Gaussian sampling                                                                                      | 86  |  |  |

|              | 5.5                                                       | FPGA implementation of the Gaussian sampler                                                                              | 87  |  |  |

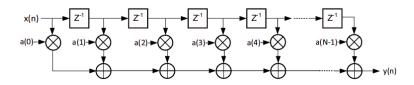

|              | 5.6                                                       | FPGA implementation of the upsampling and upconversion                                                                   |     |  |  |

|              |                                                           | $modules \ \dots $ | 92  |  |  |

|              | 5.7                                                       | Performance of the QKD transmitter                                                                                       | 94  |  |  |

| 6            | Con                                                       | aclusion and outlook                                                                                                     | 101 |  |  |

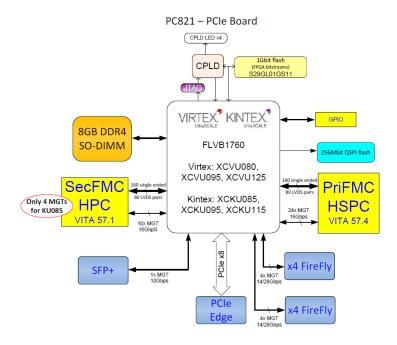

| $\mathbf{A}$ | FPO                                                       | GA and software framework                                                                                                | 103 |  |  |

|              | A.1                                                       | AXI protocol preliminaries                                                                                               | 103 |  |  |

|              | A.2                                                       | Intellectual property (IP) cores                                                                                         | 104 |  |  |

|              | A.3                                                       | FPGA and ADC/DAC boards                                                                                                  | 108 |  |  |

|              | A 4                                                       | Abaco (4DSP) framework                                                                                                   | 111 |  |  |

## Chapter 1

## Introduction

The quantum revolution started more than 100 years ago at the beginning of the 20th century with Planck's explanation of black body radiation. Planck's idea involved fundamental discrete units of electromagnetic radiation, energy quanta – photons. The discovery helped Einstein to develop a theory of the photoelectric effect not long after. It was soon realized that the new discoveries open the door to a new physics. In the following decades a completely new mathematical formalism was developed to describe the strange phenomena observed mostly in the tiny world of particles at small scales and short time frames. The famous double slit experiment revealed that photons<sup>1</sup> can still behave as a wave. This wave-particle duality is the consequence of the superposition. Superposition is one of the basic principles of quantum mechanics. It is without a classical analog and it leads to many other non-intuitive phenomena. The superposition principle was exemplified by Erwin Schrodinger with his famous thought experiment with a cat being dead and alive at the same time in a sealed box.

Another quantum mechanical effect first discovered by Einstein, Podolsky and Rosen [1], known as EPR paradox, deals with quantum systems of (at least) two particles. In their gedanken experiment two interacting particles with indeterminate momentum were to be sent far away from each other, for instance to separate ends of the galaxy. Then a measurement of one of the particles would instantly give information about the momentum of the other, because of the conservation of momentum. This would not be strange if in quantum mechanics the initial momentum of each of the particles is fundamentally without an exact value. Einstein referred to this phenomenon as a spooky action at a distance. It illustrates the non-local nature of quantum mechanics and the effect is called quantum entanglement.

In 1927 Werner Heisenberg derived his famous uncertainty principle [2] that

<sup>&</sup>lt;sup>1</sup>This effect is not exclusive to photons however.

asserts a fundamental limit to the precision with which certain pairs of physical properties of a particle, known as canonically conjugate variables, such as position and momentum, can be known. The principle stems from the same mathematical formalism as superposition and entanglement and is closely related to *no-cloning theorem* [3]. The theorem states that it is impossible to create an identical copy of an arbitrary unknown quantum state. This has big implications to quantum information theory.

Classical information theory deals with efficient coding of information for storage or for transmitting through a noisy channel. It started the information technology revolution that made huge impact in the world especially in the last several decades. Information is quantified through entropy and the basic unit is bit that takes values 0 or 1. First ideas of connecting the information theory and quantum mechanics arose in the 70s. A quantum generalization of the basic unit of information is called quantum bit or qubit. In 1984 Bennett and Brassard invented the first quantum key distribution (QKD) protocol [4] using qubits, now called BB84, after which the field saw explosive growth.

Fast forward to today, we are in the midst of the second quantum revolution [5]. The first quantum revolution gave us new rules that govern physical reality and helped shape 20th century, while the second one will take the rules and develop new technologies that should shape 21st century. The world has seen a huge increase of investments in quantum technologies in the last several years.

This work focuses on quantum communication and the most mature technologies in the field – quantum key distribution and quantum random number generation. QKD is a subfield of quantum cryptography. In a typical QKD setup, there is a transmitter (Alice) who prepares a quantum state and sends it to a receiver (Bob). The goal of such communication is generation of a classical bit-string that is a shared secret between Alice and Bob, such that there is almost no leaked information about the string values to anybody else. In a typical model, an adversary (Eve) is in control of the channel and can perform physical operations allowed by quantum mechanics. No-cloning theorem is a core principle in QKD. It assures that Eve cannot perfectly copy a quantum state generated by Alice. This means that Alice and Bob, after Bob's measurement of the state, can detect the noise introduced by Eve's snooping as she inevitably introduces the noise due to the no-cloning theorem. QKD is seen to be a (partial) replacement to the current public key distribution protocols. Today's public key infrastructure is not only completely broken by the future quantum computers [6], but the non-existence of an efficient classical algorithm that breaks the schemes has not been proved. Considering ever rising cyber security threats from hackers and governments, the increasing computational power and the fact that the world economy depends on secure cryptography, it is not hard to find motivation for developing information theoretic secure QKD systems.

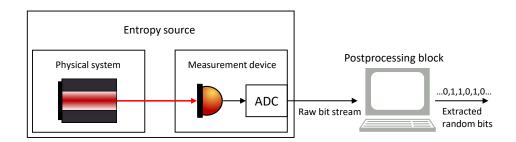

Along with quantum key distribution there is another subfield of quantum cryptography that has significant impact to both technology and fundamental science and philosophy. Quantum random number generation is a process of obtaining true random numbers. Classical physics is seen as a deterministic theory. Only quantum mechanics allows true stochastic behaviour, assuming the validity of known laws of physics. Measurements of quantum states in principle give random results that cannot be predicted by anybody in the universe. This is therefore the only way of generating information theoretic secure random numbers. Random numbers are necessary in most cryptographic protocols, including QKD. Since quantum-generated randomness is the only information-theoretic true randomness, it is a mandatory part of every QKD setup. Devices that generate quantum randomness are quantum random number generators (QRNGs).

Field programmable gate array (FPGA) is a programmable chip technology that has seen an incredible growth for the past two decades. The applications range from telecommunications to medicine. The affordability paired with incredible processing power for some purposes makes this technology very attractive for QKD and QRNG. We use a high-end FPGA to perform research in one flavour of quantum cryptography that uses continuous variables (CV). It was shown twenty years ago that quantum continues variables can be used for quantum cryptography [7]. Continuous variable quantum key distribution (CV-QKD) and continuous variable quantum random generators (CV-QRNG) are still young technologies where proof-of-principle experiments were demonstrated only recently. CV technology promises lower cost and high data rates, therefore it is a perfect place where FPGAs can show their potential.

This thesis aims to be a tiny step forward towards building a widely used technology. Its nature is inherently interdisciplinary. Building a quantum cryptography system requires knowledge in quantum optics, telecommunications, electronics and security proofs. We hope we captured the important concepts from the relevant fields, so that the thesis could be read by researchers in both fundamental science and engineering.

#### Thesis structure

This thesis consists of three main parts. The introductory chapters (1, 2 and 3) include condensed information about topics that are prerequisite for

systematic approach to QKD and QRNG. In a sense they represent the author's journey of acquiring knowledge necessary for research and technology development in the field of CV quantum cryptography. The other two parts are dedicated to the QRNG and QKD implementations in more detail.

There are six chapters in total:

- Chapter 1 is a general introduction with a brief historical overview of quantum technologies.

- Chapter 2 introduces general theoretical concepts. It consists of the basic theory of Gaussian quantum optics, following by a brief introduction to classical and quantum information theory.

- Chapter 3 is more specific and is introducing topics in CV-QKD, from the basic security model, through a description of important experimental elements, to the CV-QKD setup used as a testbed in this thesis.

- Chapter 4 is dedicated to high-rate randomness extraction and realtime entropy tests developed for our implementation of quantum random number generator. The chapter also describes a standalone implementation of the QRNG.

- Chapter 5 focuses on the FPGA implementation of the QKD transmitter. QRNG described in Chapter 4 is used as a randomness source here. Test results of the transmitter performance are presented at the end of this chapter.

- Chapter 6 gives a conclusion of the work and the outlook for the future research.

## Chapter 2

## Gaussian quantum optics and information theory

The first section of this chapter introduces basic knowledge of quantum theory of light that lays foundation for understanding continuous variable quantum cryptography. It begins with the quantization the electromagnetic field. Illustrative notions such as Wigner representation and phase space are presented. Furthermore there is a brief overview of the Gaussian states and transformations. Finally, the last section gives a short introduction to entropy and Holevo information.

#### 2.1 Introduction to Gaussian quantum optics

#### 2.1.1 Quantization of the electromagnetic field and Fock space

We start by establishing a connection between a light wave and a (quantum) harmonic oscillator [8]. Let us consider a light field confined within a cavity of length L along the z-axis and polarized along x-axis:

$$E_x(z,t) = \sqrt{\frac{2\omega^2}{V\varepsilon_0}}q(t)\sin kz, \qquad (2.1.1)$$

where  $\omega$  is the angular frequency of the light,  $k=\frac{\omega}{c}$  is the wave number, V is the cavity volume,  $\varepsilon_0$  is vacuum permittivity and c is the speed of light in vacuum. q(t) is a time dependent amplitude which is recognized as canonical position. Using Maxwell equations in vacuum the corresponding magnetic field is found:

$$B_y(z,t) = \frac{\mu_0 \varepsilon_0}{k} \sqrt{\frac{2\omega^2}{V \varepsilon_0}} \dot{q}(t) \cos kz, \qquad (2.1.2)$$

## CHAPTER 2. GAUSSIAN QUANTUM OPTICS AND INFORMATION THEORY

where  $p(t) = \dot{q}(t)$  is canonical momentum and  $\mu_0$  is vacuum permeability. The energy of this field is given by its Hamiltonian (in units where the speed of light is c = 1)

$$H = \frac{1}{2}(p^2 + \omega^2 q^2). \tag{2.1.3}$$

Hamiltonian of the same form is found in a harmonic oscillator with the unit mass. Quantization of the harmonic oscillator is known procedure, so generalized position and momentum operators, and the ladder operators, are defined [9]. Quantum Hamiltonian of the field is

$$\hat{H}_k = \hbar \omega_k (\hat{a}_k^{\dagger} \hat{a}_k + \frac{1}{2}) = \frac{1}{2} (\hat{p}_k^2 + \omega_k^2 \hat{q}_k^2), \tag{2.1.4}$$

where  $\hbar$  is the reduced Planck constant and  $\hat{a}_k^{\dagger}$  and  $\hat{a}_k$  are creation and annihilation operators respectively

$$\hat{a}_k^{\dagger} = \frac{1}{\sqrt{2\hbar\omega}} (\omega \hat{q}_k - i\hat{p}_k), \qquad (2.1.5)$$

$$\hat{a}_k = \frac{1}{\sqrt{2\hbar\omega}} (\omega \hat{q}_k + i\hat{p}_k). \tag{2.1.6}$$

Here an index k is introduced which denotes a mode of the electromagnetic field. The notion of mode is found in different contexts and it is good to point out the right meaning for a particular case. Modes are orthogonal solutions for the propagation equations of light [10]. Two types of modes can be distinguished:  $spatial\ modes$  define a pattern of the field in the plane orthogonal to the polarization, and  $temporal\ modes$  which relate to time and frequency. When light is interfering, polarization is important, so sometimes polarization modes are also defined. In the case of this analysis, the index k denotes a frequency of the harmonic oscillator, or in other words, frequency mode of the light wave in the cavity described by equations 2.1.1 and 2.1.2.

The number operator of a mode is defined as  $\hat{n}_k = \hat{a}_k^{\dagger} \hat{a}_k$ . Eigenstates of the number operator are states with exact number of photons. These states span a Fock space  $|n_k\rangle$ . The ladder operators could also be defined by their action on a Fock state [12, 25]

$$\hat{a}_k^{\dagger} | n_k \rangle = \sqrt{n_k + 1} | n_k + 1 \rangle, \qquad (2.1.7)$$

$$\hat{a}_k |n_k\rangle = \sqrt{n_k} |n_k - 1\rangle, \quad \hat{a}_k |0\rangle = 0,$$

(2.1.8)

$$\hat{a}_k^{\dagger} \hat{a}_k | n_k \rangle = n_k | n_k \rangle. \tag{2.1.9}$$

Canonical position and momentum can be conversely defined using the ladder operators:

$$\hat{q}_k = \sqrt{\frac{\hbar}{2\omega_k}} (\hat{a}_k + \hat{a}_k^{\dagger}), \qquad (2.1.10)$$

$$\hat{p}_k = -i\sqrt{\frac{\hbar\omega_k}{2}}(\hat{a}_k - \hat{a}_k^{\dagger}). \tag{2.1.11}$$

For these operators, the following commutations relations hold:

$$[\hat{q}_k, \hat{p}_{k'}] = i\hbar \delta_{kk'}, \quad [\hat{a}_k, \hat{a}_{k'}^{\dagger}] = \delta_{kk'}, \quad [\hat{a}_k, \hat{a}_{k'}] = 0,$$

(2.1.12)

where  $\delta_{kk'}$  is Kronecker delta. One can see that the position and momentum are real and imaginary part of the annihilation operator respectively. Dimensionless counterparts of the position and momentum are defined

$$\hat{Q}_k \equiv \sqrt{\frac{\omega_k}{2\hbar}} \hat{q}_k, \quad \hat{P}_k \equiv \frac{1}{\sqrt{2\omega_k\hbar}} \hat{p}_k.$$

(2.1.13)

Measuring these variables one gets classical quadratures of the mode k, i.e. they represent real and imaginary parts of the complex amplitude [9]. The commutation relation for these operators is:

$$[\hat{Q}_k, \hat{P}_{k'}] = \frac{i}{2} \delta_{kk'} \tag{2.1.14}$$

This is the same as if condition  $\hbar = 1/2$  is put to the commutation relation in equation 2.1.12. Since the two variables are not commuting, the uncertainties of measurements of both quadratures at the same time obey Heisenberg's relation:

$$\langle (\Delta \hat{Q}_k)^2 \rangle \langle (\Delta \hat{P}_k)^2 \rangle \ge \frac{1}{4} |\langle [\hat{Q}_k, \hat{P}_k] \rangle|^2 = \frac{1}{16}, \tag{2.1.15}$$

where  $\langle (\Delta \hat{Q}_k)^2 \rangle$  is the variance of operator  $\hat{Q}_k$ . This means that measuring both quadratures at the same time with perfect precision is not possible and this fact has a profound impact to continuous variable quantum protocols.

For the purpose of connecting the mean number of photons in a mode with the measured quadratures, it is useful to define the number operator using quadrature operators:

$$\hat{n}_k = \hat{a}_k^{\dagger} \hat{a}_k = \hat{Q}_k^2 + \hat{P}_k^2 - \frac{1}{2}. \tag{2.1.16}$$

Quadrature operators are observables with continuous eigenspectra. Their eigenvalues are continuous and real,  $Q, P \in \mathbb{R}$  and their eigenstates  $|Q\rangle$  and  $|P\rangle$  identify two bases which are connected with Fourier transform (for mode k):

$$\hat{Q}_k |Q_k\rangle = Q_k |Q_k\rangle, \quad \hat{P}_k |P_k\rangle = P_k |P_k\rangle,$$

(2.1.17)

$$|Q_k\rangle = \frac{1}{2\sqrt{\pi}} \int dP_k e^{-iQ_k P_k/2} |P_k\rangle, \quad |P_k\rangle = \frac{1}{2\sqrt{\pi}} \int dQ_k e^{iQ_k P_k/2} |Q_k\rangle.$$

(2.1.18)

The vectors in the bases are orthogonal and complete:

$$\langle Q_k | Q_k' \rangle = \delta(Q_k - Q_k'), \quad \langle P_k | P_k' \rangle = \delta(P_k - P_k'),$$

(2.1.19)

$$\int_{-\infty}^{\infty} |Q_k\rangle \langle Q_k| \, dQ_k = 1, \quad \int_{-\infty}^{\infty} |P_k\rangle \langle P_k| \, dP_k = 1. \tag{2.1.20}$$

It is worth noting that quadrature eigenstates are not square-integrable and are unphysical.  $^{1}$

#### 2.1.2 Phase space representation

Information about a physical system is contained in its quantum state defined by its density operator  $\hat{\rho}$ . The density operator is a positive operator with the unit trace. The operator can be defined for N-mode system and it represents the mapping  $\hat{\rho}: \mathcal{H}^{\otimes N} \to \mathcal{H}^{\otimes N}$ . An equivalent representation of quantum states that lies in *phase space* (also called quadrature or symplectic space) is Wigner function. It is a quasi-probability distribution defined over phase space and it mostly behaves as a normal probability distribution, though it can have negative values. It was first proposed in a paper from 1932 by Wigner [11].

#### Definition 2.1.1. (Wigner function)

$$W(x) = \frac{1}{(2\sqrt{\pi})^{2N}} \int_{\mathbb{R}^{2N}} d^{2N} \xi e^{-ix\Omega \xi/2} \chi(\xi), \qquad (2.1.21)$$

where  $\chi(\boldsymbol{\xi})$  is Wigner characteristic function that is defined as  $\chi(\boldsymbol{\xi}) = \text{Tr}[\hat{\rho}D(\boldsymbol{\xi})]$  where  $D(\boldsymbol{\xi}) = \exp(i\boldsymbol{x}\Omega\boldsymbol{\xi})$  is Weyl operator[12]. The vector  $\boldsymbol{x}$  is the vector of quadrature operators of N modes, and  $\Omega$  is the matrix that defines commutation relations  $[\boldsymbol{x}_i, \boldsymbol{x}_j] = i2\Omega_{ij}$ .

Let W(Q, P) be a Wigner function of a one-mode state (here we drop index k for simplicity). Even though the function is not a real probability

<sup>&</sup>lt;sup>1</sup>It is impossible to produce a light field with state  $|Q_k\rangle$  or  $|P_k\rangle$  for some  $Q_k, P_k \in \mathbb{R}$ . This would mean infinite *squeezing* (see the following section).

distribution, it resembles it in some properties and is very convenient for depicting different bosonic states. The function is normalized:

$$\int W(Q, P)dQdP = 1. \tag{2.1.22}$$

By integrating over a quadrature, one gets the probability distribution for the other one

$$\int W(Q, P)dQ = \langle P | \hat{\rho} | P \rangle, \quad \int W(Q, P)dP = \langle Q | \hat{\rho} | Q \rangle. \quad (2.1.23)$$

Wigner function W(Q, P) can also be defined as a function of a complex variable  $W(\alpha)$ , where  $\alpha = Q + iP$ . This variable is called the complex amplitude. It can be seen from 2.1.16 that  $\hat{n} = \alpha^2$  (again we dropped the index k denoting a mode). Given the fact Wigner function behaves like a probability distribution, important parameters of a quantum state are the statistical moments. The first moment, also called the *displacement vector* is the mean value of the vector  $(\mathbf{x})$ :

$$\bar{\boldsymbol{x}} = \langle \boldsymbol{x} \rangle = \text{Tr}(\boldsymbol{x}\hat{\rho})$$

(2.1.24)

The second moment is in matrix form and is called the *covariance matrix* V whose elements are defined as:

$$V_{ij}^{\kappa} = \frac{1}{2} \langle \{ \Delta \hat{x}_i^{\kappa}, \Delta \hat{x}_j^{\kappa} \} \rangle, \qquad (2.1.25)$$

where  $\Delta \hat{x}_i^{\kappa} \equiv \hat{x}_i^{\kappa} - \langle \hat{x}_i^{\kappa} \rangle$ . Here  $\hat{x}_i^{\kappa}$  is an element of  $\boldsymbol{x}$  where  $\kappa$  counts the two quadratures.  $\{,\}$  is the anti-commutator. Clearly, the diagonal elements of the covariance matrix are the variances of the quadratures:

$$V_{ii}^{\kappa} = V(\hat{x}_i^{\kappa}) = \langle \hat{x}_i^{\kappa 2} \rangle - \langle \hat{x}_i^{\kappa} \rangle^2, \tag{2.1.26}$$

The most important class of states for our work are the states that are fully described by the first two moments. They are called *Gaussian states* since the Wigner function for these states has a Gaussian shape:

$$W(\boldsymbol{x}) = \frac{1}{(2\pi)^N \sqrt{\det \boldsymbol{V}}} e^{-\frac{1}{2}(\boldsymbol{x} - \bar{\boldsymbol{x}})^T \boldsymbol{V}^{-1}(\boldsymbol{x} - \bar{\boldsymbol{x}})}.$$

(2.1.27)

#### 2.1.3 Gaussian states

A state with zero photons  $|0\rangle$  or the *vacuum state* is a Gaussian state. Annihilating a photon from the vacuum state gives the same state, hence the vacuum state is an eigenstate of the annihilation operator with zero eigenvalue  $\hat{a}|0\rangle = 0$ . The covariance matrix of such state is identity V = 1,

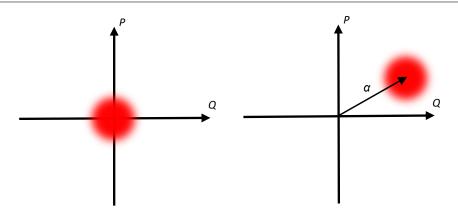

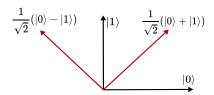

Figure 2.1: Vacuum state and displaced state (coherent state) in phase space

therefore the variances of the quadratures are 1. This state is symmetrical and the variances are a consequence of the uncertainty principle. This uncertainty causes a noise when measuring the quadratures. This noise is called *shot noise* or *vacuum noise*. Shot noise is one of the central concepts in continuous variable quantum key distribution and quantum random number generation.

The displacement operator is a Weyl operator for the complex variable  $\alpha$ . This operator 'displaces' the vacuum state in the phase space. Fig. 2.1 shows the Wigner function of the vacuum state and a displaced state in the phase space. Displaced vacuum state is called the *coherent state* and is characterized by its complex amplitude  $|\alpha\rangle = D(\alpha)|0\rangle$ . The covariance matrix of the coherent state stays identity, but the mean values of the quadratures are now  $\bar{x} = (Q, P)^T$ .

Coherent states [13] were discovered by Scroedinger in 1926 when he was solving his equation with the aim of finding a solution for quantum harmonic oscillator that is asymptotically close to classical states. They are the states with the smallest possible uncertainty. Intuitively, they are the closest to perfectly noiseless classical states.

Coherent states are the eigenstates of the annihilation operator:

$$\hat{a} |\alpha\rangle = \alpha |\alpha\rangle. \tag{2.1.28}$$

In the number basis, coherent states are expanded as:

$$|\alpha\rangle = e^{-\frac{1}{2}|\alpha|^2} \sum_{n=0}^{\infty} \frac{\alpha^n}{\sqrt{n!}} |n\rangle.$$

(2.1.29)

The mean energy of a coherent state is

$$\langle H \rangle = \langle \alpha | H | \alpha \rangle = \hbar \omega \langle \alpha | \hat{a}^{\dagger} a + \frac{1}{2} | \alpha \rangle = \hbar \omega (|\alpha|^2 + \frac{1}{2}).$$

(2.1.30)

As we have seen, the number states  $|n\rangle$  form an orthogonal basis. This is not the case with coherent states as they are not mutually orthogonal and form an overcomplete basis. The overlap between two coherent states is

$$|\langle \beta | \alpha \rangle|^2 = e^{-|\beta - \alpha|^2}. \tag{2.1.31}$$

It was shown that coherent states are symmetrical in the phase space as the variances of the both quadratures are the same. The uncertainty principle does not forbid a quadrature variance to be smaller than 1 (in natural units) as long as the other quadrature variance increases. Such states exist and they are called *squeezed states*. They can be produced by pumping a nonlinear crystals with a bright laser. Even though there are quantum cryptography protocols using the squeezed states [14], they are not the focus of this thesis, and due to experimental complexities, this field is yet to be explored in more depth [15, 16].

Thermal state is a mixture of eigenstates of a Fock space. This state is Gaussian and in Fock space it is represented with the density operator

$$\hat{\rho}(\bar{n}) = \sum_{n=0}^{+\infty} \frac{\bar{n}^n}{(\bar{n}+1)^{n+1}} |n\rangle \langle n|, \qquad (2.1.32)$$

where  $\bar{n} = \text{Tr}(\hat{\rho}\hat{n})$  is the mean number of photons in the bosonic mode. It can be shown that thermal states maximize the von Neumann entropy  $S = -\text{Tr}(\hat{\rho}\log\hat{\rho})$ . Their Wigner function is Gaussian with zero mean and covariance matrix  $V = (2\bar{n} + 1)\mathbb{1}$ .

#### 2.2 Classical information theory

Classical information theory was born in 1948 with the work of Claude Shannon [17]. There is a vast number of resources on the topic. Definitions in the following paragraphs can be found in [18].

The starting point is Shannon entropy:

**Definition 2.2.1.** (Shannon entropy). Let there be a random variable A, with alphabet A that is distributed according to the probability distribution

<sup>&</sup>lt;sup>2</sup>Von Neumann entropy is defined in Section 2.3.

## CHAPTER 2. GAUSSIAN QUANTUM OPTICS AND INFORMATION THEORY

$P_A(a), a \in \mathcal{A}$ . Shannon entropy of the random variable is defined as

$$H(A) = -\sum_{a \in A} P_A(a) \log P_A(a).$$

(2.2.1)

Entropy quantifies the average uncertainty about a stochastic source. If the variable is continuous, the sum becomes an integral

$$H(A) = -\int_{\mathcal{S}} P_A(a) \log P_A(a) da, \qquad (2.2.2)$$

where S is the support of the random variable A, i.e. it is the subset of A for which P(a) > 0.

The joint entropy of two discrete random variables A and B with alphabets A and B respectively is

$$H(AB) = -\sum_{a \in \mathcal{A}} \sum_{b \in \mathcal{B}} P_{AB}(a, b) \log P_{AB}(a, b). \tag{2.2.3}$$

Conditioning distribution A on the outcomes of distribution B, one gets the conditional entropy

$$H(A|B) = H(AB) - H(B) = -\sum_{a \in A} \sum_{b \in B} P_{AB}(a|b) \log P_{AB}(a|b).$$

(2.2.4)

Now the mutual information between the two variables can be defined. Mutual information quantifies the amount of information one obtains about a random variable when observing another.

$$I(A:B) = H(A) - H(A|B).$$

(2.2.5)

Shannon entropy quantifies the amount of randomness of a randomness source on average, which means it is asymptotic in nature. A generalization of Shannon entropy is  $R\acute{e}nyi\ entropy$ :

**Definition 2.2.2.** Rényi entropy of order  $\alpha$ , where  $\alpha \geq 0$  and  $\alpha \neq 1$  is defined as

$$H_{\alpha}(A) = \frac{1}{1-\alpha} \log \left( \sum_{a \in \mathcal{A}} P_A(a)^{\alpha} \right). \tag{2.2.6}$$

Shannon entropy is obtained as a special case of Rényi entropy when  $\alpha \to 1$ . Another special case of Rényi entropy is *min-entropy* when the parameter converges to infinity  $\alpha \to \infty$ :

**Definition 2.2.3.** (Min-entropy) The min-entropy  $H_{\min}(A)$  (also often denoted  $H_{\infty}$  in literature) of A is

$$H_{\min}(A) = \min_{a \in \mathcal{A}} \log \frac{1}{P_A(a)}.$$

(2.2.7)

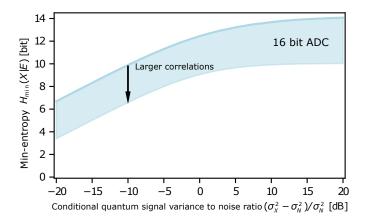

Min-entropy is important quantity in quantum cryptography as it is the main measure of randomness of a finite bit array. It is used in both quantum key distribution to quantify the amount of secret bits shared by Alice and Bob [19], and quantum random number generation and randomness extraction [20, 21] to quantify the amount of randomness in a finite QRNG output. While Shannon entropy tells how many random bits are in a sample on average, the min-entropy gives the lower bound on the number of random bits in every sample.

#### 2.3 Quantum information theory

Quantum information theory is an extension of Shannon theory by including the quantum formalism. A good resource in this field is [22].

The quantum analogy of Shannon entropy is von Neumann entropy, defined for a quantum state  $\hat{\rho}$ .

#### Definition 2.3.1. (Von Neumann entropy)

$$S(\hat{\rho}) = -\operatorname{Tr}(\hat{\rho}\log\hat{\rho}),\tag{2.3.1}$$

where Tr is the trace of an operator.

Von Neumann entropy can be seen as a measure of uncertainty after measuring the quantum state  $\hat{\rho}$ . For example, if a pure state (where  $\text{Tr}(\hat{\rho}^2) = 1$ ) is measured in appropriate basis, no uncertainty remains, therefore  $S(\hat{\rho}) = 0$ . The entropy is invariant under unitary operations

$$S(\hat{\rho}) = S(\hat{U}\hat{\rho}\hat{U}^{\dagger}). \tag{2.3.2}$$

This means von Neumann entropy remains unchanged under Gaussian unitaries. For separable states (of modes A and B) the entropy is additive

$$S(\hat{\rho}_A \otimes \hat{\rho}_B) = S(\hat{\rho}_A) + S(\hat{\rho}_B). \tag{2.3.3}$$

For a two-mode state  $\hat{\rho}_{AB}$  one can define the joint entropy

$$S(\hat{\rho}_{AB}) = -\operatorname{Tr}(\hat{\rho}_{AB}\log\hat{\rho}_{AB}). \tag{2.3.4}$$

If the partial trace is defined (over mode B and similarly for A) of the two-mode state  $\hat{\rho}_A = \text{Tr}_B \, \hat{\rho}_{AB}$ , then the marginal entropies are:

$$S(\hat{\rho}_A) = -\operatorname{Tr}(\hat{\rho}_A \log \hat{\rho}_A), \tag{2.3.5}$$

$$S(\hat{\rho}_B) = -\operatorname{Tr}(\hat{\rho}_B \log \hat{\rho}_B). \tag{2.3.6}$$

The conditional von Neumann entropy is defined analogously to its classical counterpart:

$$S(A|B) = S(AB) - S(B). (2.3.7)$$

## CHAPTER 2. GAUSSIAN QUANTUM OPTICS AND INFORMATION THEORY

Similarly the quantum mutual information be defined. A quantity that is important in QKD and QRNG security formalism, and does not have a classical analog, is *Holevo information*. It is also called Holevo bound and it establishes the upper bound to the amount of information that can be known about a quantum state.

**Definition 2.3.2.** (Holevo information) Let a transmitting party prepare a set of quantum states  $\{\hat{\rho}_B^j\}$  with probability  $P_A(j)$ , so the receiving party receives the state  $\hat{\rho}_B = \sum_j P_A(j)\hat{\rho}_B^j$ . Then the amount of information extractable by an optimal measurement of the state  $\hat{\rho}_B$  is bounded by Holevo information

$$\chi(A:B) = S(\hat{\rho}_B) - \sum_{j} P_A(j)S(\hat{\rho}_B^j).$$

(2.3.8)

For example, this quantity is calculated in QKD protocols with respect to eavesdropper's quantum system in order to upper bound the accessible information of the secret key to her.

## Chapter 3

# Introduction to continuous variable quantum key distribution

#### 3.1 Security of CV-QKD

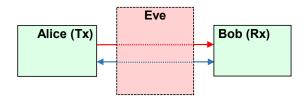

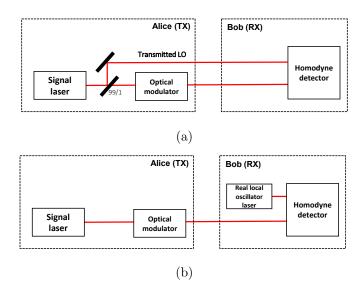

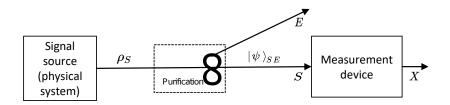

Even though theoretical security formalism is not the focus of this thesis, it is important to be aware of security notions as, in the end, the goal of our work is implementation of secure quntum cryptographic systems. This section gives an overview of security concepts in CV-QKD systems with coherent states. The core principle of QKD security is the quantum no-cloning theorem. The theorem forbids perfect copying of an arbitrary quantum state with the unit probability. This means that quantum states sent by Alice (transmitter) will be disturbed (on average) if measured by Eve (eavesdropper) on their way to Bob (receiver)(Fig. 3.1<sup>1</sup>). As the no-cloning theorem assumes arbitrary states. Alice needs a source of true randomness at her disposal. Using CV-QKD protocols based on coherent states, the information is encoded into the quadrature of the transmitted light. When Eve tries to eavesdrop by intercepting a portion of the transmitted light, she inherently introduces noise which is subsequently detected by Bob as he receives the signal. Eve's optimal strategies for measuring quantum states, in order to gain as much information as possible, are known and are subject of research in quantum cloning [23]. We can put together a standard list of attacks often found in the literature, that Eve can perform on the quantum state that Alice is sending. The attacks are listed from the weakest to the most powerful [19, 24, 25]:

<sup>&</sup>lt;sup>1</sup>In this thesis we are working only with prepare-and-measure protocols where Alice prepares a quantum state and sends it to Bob who measures it. On the other hand there are *entanglement-based* protocols where Alice prepares a two-mode state and keeps and measures one half of the state, while the other is sent to Bob.

## CHAPTER 3. INTRODUCTION TO CONTINUOUS VARIABLE QUANTUM KEY DISTRIBUTION

Figure 3.1: Three parties in a *prepare-and-measure* QKD protocol: Alice (transmitter) and Bob (receiver) are trusted, while Eve (eavesdropper) is the untrusted party who controls the channel. Unidirectional quantum channel (from Alice to Bob) is designated by the red line and bidirectional authenticated classical channel is designated by the blue line.

- Individual attack Eve performs independent and identically distributed (i.i.d.) attack on each pulse separately. She measures her quantum states before Bob performs post-processing steps.

- Collective attack Eve performs an i.i.d. attack and measures her state collectively after Bob performs post-processing steps.

- Coherent attack Eve couples a pre-entangled multimode ancilla with all the pulses from Alice. She optimally measures her system after Bob performs post-processing. This should be the most powerful attack and notoriously hard to implement in real world.

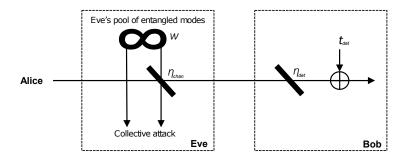

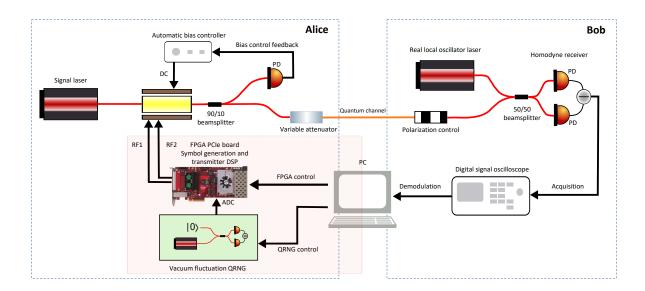

Fig. 3.2 shows a model of collective attack to a CV-QKD system. This model is used for proving security to the CV-QKD system used as an experimental testbed for the QKD transmitter developed for the thesis. The channel is fully controlled by Eve, so the losses and the noise of the channel are untrusted. Trusted loss and noise originating from inside Bob's box are also defined and are quantified during receiver calibration.

First continuous variable QKD protocols proven to be secure were protocols with squeezed states [26, 27], shortly followed by the first protocol with coherent states [28]. For all the earlier protocols, security was proven in the asymptotic regime where Alice sends an infinite number of pulses to Bob, so the quantum state is exactly defined by obtained average parameters. The Devetak-Winter formula gives the key rate for asymptotic regime and collective attacks [29]:

$$R_{\text{coll}}^{\text{asymptotic}} = \beta I(A:B) - \chi(B:E).$$

(3.1.1)

The key rate is the classical mutual information between Alice's and Bob's symbols reduced by Holevo information between Bob's and Eve's quantum system.  $\beta$  is reconciliation efficiency. These quantities are calculated within a security model and are a function of trusted and untrusted noise and

Figure 3.2: QKD model under optimal entangling cloner collective attack. Eve prepares a pool of entangled Gaussian modes and injects one part of the entangled state to the channel.  $\eta_{\text{chan}}$  – channel transmittance modelled with a beamsplitter (untrusted loss). w – the variance of each of the Eve's modes.  $\eta_{\text{det}}$  – detector transmittance (trusted loss).  $t_{\text{det}}$  – variance of trusted noise. The variance of the untrusted noise at the detector is  $\eta_{\text{det}}(1-\eta_{\text{chan}})w$ .

loss. Information reconciliation is a post-processing step where Alice and Bob use an error correcting code (such as a LDPC code) to match the data strings obtained after Bob's measurement. In the equation above the reverse reconciliation is used, where Alice is changing her data to match Bob's, after Bob provides the error correction syndrome through authenticated classical channel. It has been proven that the reverse reconciliation is better than the direct reconciliation [30], in which case Holevo information would be calculated between Alice's and Eve's state:  $\chi(A:E)$ . In CV-QKD protocols with coherent states and Gaussian modulation, Alice and Bob can calculate the covariance matrix  $V_{AB}$  of the bipartite state  $^2$   $\rho_{AB}$ . The upper bound on the Holevo information is a function of the covariance matrix. The matrix values depend on transmissivity and noise in the system.

There are three main steps in post-processing:

- Parameter estimation After Bob performs the measurement of the quantum state sent by Alice, the two choose a random set of symbols for which they calculate the covariance matrix  $V_{AB}$  in order to get the upper bound for  $\chi(B:E)$ .

- Information reconciliation Bob sends the error correction syndrome to Alice. Some information is leaked to Eve in this step.

$<sup>^2</sup>A$  are the symbols Alice sends, and B are the symbols Bob receives.  $\rho_{AB}$  is generally calculated in the entanglement-based scheme where Alice obtains her symbols by measuring one part of two-mode squeezed vacuum state while the other part is sent to Bob. Such a scheme is proven to be equivalent to prepare-and-measure and it is used due to the fact it is easier to prove security this way.

## CHAPTER 3. INTRODUCTION TO CONTINUOUS VARIABLE QUANTUM KEY DISTRIBUTION

• Privacy amplification After reconciling, Alice and Bob share identical strings. Eve has some information about it, therefore a privacy amplification protocol is performed to reduce Eve's information about the secret key to a negligible value. Most often, universal hashing is used for this step, same as with randomness extraction for QRNGs, however with much larger block lengths.

In the last years there has been a great progress in proving security of Gaussian modulated CV-QKD for the finite regime (finite key instead of infinite one) and proving the optimality of Gaussian collective attacks [31, 32].

#### 3.2 Building blocks in CV-QKD experiments

Here we describe telecommunication components used for CV-QKD. Alice's system consists of:

- **Signal laser** produces coherent light beam which is the carrier of information.

- Optical modulator modulates the laser light and therefore encode information in the carrier.

- Bias controller an electrical device that applies slow changing bias volages to the modulator, thus making sure the modulator works at a desired set point so the signal inputs to the modulator are translated to proper optical modulation.

- Symbol generator generates data symbols in the baseband and is connected to a DSP block that is in turn connected to the input of the modulator. In the case of our CV-QKD system, the symbols are generated in field-programmable gate array (FPGA) chips using random numbers generated by the QRNG.

Bob's receiver consists of devices that are used to extract transmitted symbols from the optical channel. Bob's system consists of:

- Local oscillator laser used as a phase reference to the input optical signal.

- **Homodyne detector** used to optically mix the local oscillator and the input signal in order to 'filter out' the optical bandwidth of interest. It uses photodiodes and transimpedance amplifiers to convert optical power to voltage.

- **Signal processing block** an electrical device that does the electrical and digital post-processing (phase recovery, demodulation etc.) in

order to recover transmitted symbols. CPU, GPU or FPGA-based processing systems are used for this purpose.

#### 3.2.1 Lasers

Laser is a source of light and therefore the key component in optical experiments. For the purpose of our experiments, we consider laser to be the source of coherent states of light. It may also be regarded as a source of a single mode of radiation.

Laser consists of a narrow band optical amplifier which generates a well defined optical beam in both frequency and spatial domains. We use continuous wave (CW) (in contrast to pulse lasers) that produce a steady output beam. Geometrical properties of the beam are matched to spatial modes of the laser cavity.

There are several parameters that are important for characterizing a laser: optical power, spatial mode structure, output wavelength, frequency spectrum and noise spectrum [33]. Spatial properties of the beam are determined by the optical resonator. Generally, a single spatial mode that also the simplest one  $\text{TEM}_{0,0}$  is of interest. One of the goals of CV-QKD is to use the off-the-shelf telecommunication equipment [24]. Therefore, the laser wavelength would generally be in one of the standard telecom windows such as 1550nm or 1310nm [34] .

#### 3.2.2 Beamsplitters and couplers

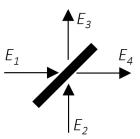

One of the most common elements in free-space optical experiments is the beamsplitter. Fiber couplers are equivalent devices in fiber optics. A beamsplitter<sup>3</sup> can be modelled as semi transparent mirror with reflectivity and transmissivity coefficients r and t. For an input beam with classical complex amplitude  $E_1$  there are two output beams, one reflected  $E_3$ , the other transmitted  $E_4$  as it is shown in Fig. 3.3. Generally, beamsplitters have two inputs, as another input with amplitude  $E_2$ , propagating from direction shown in the Fig. 3.3, will produce at the output a wave in the same place and propagating in the same direction as  $E_3$  and  $E_4$  [33]. The reflectivity and transmissivity coefficients give the ratio of the amplitudes of the input and output fields (in convenient matrix form):

$$\begin{pmatrix} E_3 \\ E_4 \end{pmatrix} = \begin{pmatrix} r_{31} & t_{32} \\ t_{41} & r_{42} \end{pmatrix} \begin{pmatrix} E_1 \\ E_2 \end{pmatrix}, \tag{3.2.1}$$

<sup>&</sup>lt;sup>3</sup>Even though we do not perform free-space optical experiments, in the context of mathematical analysis, it is common to talk about beamsplitters and not fibre couplers.

## CHAPTER 3. INTRODUCTION TO CONTINUOUS VARIABLE QUANTUM KEY DISTRIBUTION

Figure 3.3: Representation of a lossless beamsplitter showing the notation for electric field amplitudes of the input and output beams.

where  $r_{31,42}$  and  $t_{32,41}$  are complex numbers whose values are determined by using energy conservation law and boundary conditions in the dielectric mirror materials [35]. In our experiments we use the balanced beamsplitter, also called 50/50 beamsplitter, where  $|r_{31,32}|^2 = |t_{41,42}|^2 = 1/2$ .

In the expression above, we consider the beamsplitters to be ambiguous to input beam polarizations. There are however polarizing beamsplitters (PBSs) that reflect only one polarization and transmit the orthogonal polarization [33]. In general, the coefficients for PBS are not trivial, they depend on the polarization. They are used in *polarization diverse receivers* [45]. Such receivers are expected to be used in future CV-QKD designs as the technology matures.

#### 3.2.3 Modulators

In telecommunications and electronics, modulation is a process of changing one or more properties of a periodic signal (generally a sine wave) called *the carrier signal*. In optical telecommunications the carrier is typically a strong laser light. *Modulator* is a device that performs modulation. As an input, it takes the carrier and *the modulating* signal, which carries information to be transmitted. Most often the modulator changes one of the three parameters of the carrier – amplitude (amplitude modulation -AM), frequency (FM) or phase (PM).

Historically, in classical optical telecommunications, there was a period when both researchers and industry focused mostly on relatively simple amplitude modulated, or in this case more often called *intensity modulated* (IM) optical systems, with *direct detection* (DD) [36]. Owing to simplicity these systems were cheap and also provided high rates. Direct detection means that the information bit is inferred by directly detecting signal power during the symbol interval. However, by introducing coherent detection schemes, one is able to use more complicated and spectral efficient modulation tech-

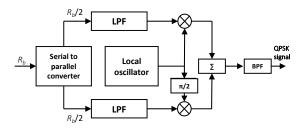

Figure 3.4: Electrical QPSK modulator block diagram. LPF: low-pass filter, BPF: band-pass filter

niques [37].

One such modulation scheme is quadrature phase shift keying (QPSK). In this scheme two phase shifted carriers are independently modulated by two independent modulating signals and added at the output. The block diagram is shown in Fig. 3.4. The two carriers are shifted by  $\pi/2$ , therefore the two modulating signals are the quadratures of the output signal. The output signal can be described with the following expression:

$$\alpha_{\text{out}}(t) = \alpha_0 q(t) \cos(\omega t) + \alpha_0 p(t) \sin(\omega t), \qquad (3.2.2)$$

where  $\alpha_0$  is the fixed amplitude and q(t) and p(t) are quadrature digital signals, which for QPSK take values  $q(t), p(t) \in \{-1, 1\}$ . A figure of merit that is often used to characterize the performance of a system with QPSK modulation is the *error vector magnitude* (EVM). The error vector is defined as a vector in phase space (quadrature IQ plane) between the ideal constellation point and the point received by receiver. EVM is defined as a percentage

$$EVM(\%) = \sqrt{\frac{P_{error}}{P_{reference}}} \times 100\%, \tag{3.2.3}$$

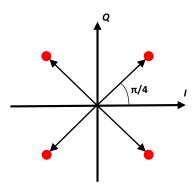

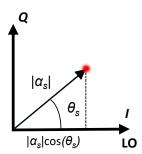

where  $P_{\rm error}$  is the power of the error vector and  $P_{\rm reference}$  is the power of the reference signal. Fig. 3.5 shows QPSK constellation in the phase space. It is important to note that QPSK modulator is the general quadrature modulator, since by changing the modulating signals q and p one is able to achieve different quadrature modulation schemes including the Gaussian one used in QKD setup in this thesis. It is common that the modulators are called the IQ modulators since the two quadratures are denoted as I – 'the in-phase component', and Q – 'the quadrature component'. We use this notation in the following chapters.

#### Optical IQ modulator

Modulators in optics are realized using crystals with electro-optical characteristics where the refractive index can be manipulated by applying external electric field [38]. This property leads directly to optical phase modulation.

Figure 3.5: QPSK constellation in phase space. Here we introduce a notation that is common in telecommunication where the quadratures are denoted I and Q instead of Q and P respectively.

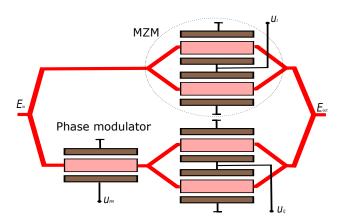

Figure 3.6: IQ modulator

By putting two phase modulators in parallel while using two optical couplers for splitting the input beam and combining the two beams at the output, one gets the Mach-Zehnder modulator (MZM) (encircled in Fig. 3.6). MZM can be operated in two modes: push-push where MZM behaves as a pure phase modulator, and push-pull where MZM behaves as a pure amplitude modulator. The quadrature point is a voltage configuration of MZM where the transfer characteristics of the modulator can be considered linear with respect to the input bias voltages. By putting together two MZMs and a phase modulator one gets the optical IQ modulator shown in Fig. 3.6. The phase modulator shifts the phase by  $\pi/2$ , therefore creating two orthogonal carriers in the two arms of the interferometer. Two MZMs act as amplitude modulators.  $u_I(t)$  and  $u_Q(t)$  are bias voltages which are also input modulating signals for the two quadratures. The transfer function

of the modulator with linear approximation around the quadrature point is:

$$\frac{E_{\text{out}}(t)}{E_{\text{in}}(t)} = \frac{\pi}{4V_{\pi}} u_I(t) + i \frac{\pi}{4V_{\pi}} u_Q(t)$$

(3.2.4)

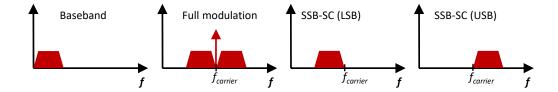

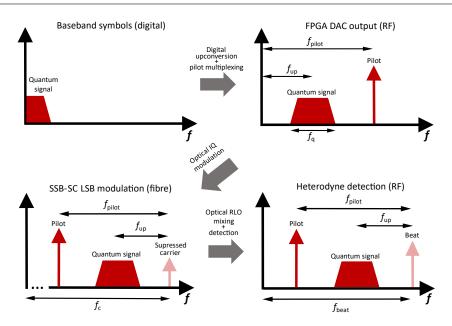

A feature of IQ modulators is their ability to create single-sideband modulation (SSB). SSB modulation was used for a long time in radio frequency, microwave and optical telecommunication. Its primary purpose is to reduce the bandwidth of transmitted signal by a factor of two, therefore reducing noise and increasing signal-to-noise (SNR) ratio and bandwidth efficiency. Furthermore, SSB modulation uses less power to transmit the same amount of information compared to a two-sided modulation. The reduction of power can be achieved also by manipulating the carrier, so there is a difference between SSB with full carrier and SSB with suppressed carrier (SSB-SC). Sometimes it is favorable that the carrier is present for easier carrier recovery and synchronization at the receiver. Single sideband modulation is graphically depicted in Fig. 3.8.

Given a real signal E(t) with double-sideband (DSB) spectrum, the SSB version of the signal is obtained by the following operation:

$$E_{SSB}(t) = E(t) \pm i\hat{E}(t) \tag{3.2.5}$$

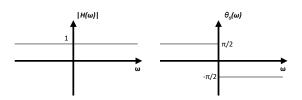

where plus sign gives the lower sideband (LSB), while minus sign gives the upper sideband (USB). By  $\hat{E}(t)$  is denoted the Hilbert transform of the signal. A Hilbert transformation is defined in frequency domain as a fixed phase shift depending on the frequency sign. The modulo of the amplitude characteristics of the Hilbert transform is unity for all frequencies  $|H(\omega)| = 1$ , and the phase characteristics is  $\theta_H(\omega) = \text{sgn}(\omega)\frac{\pi}{2}$  as shown in Fig. 3.7[39]. Using the previous analysis and the properties of Fourier transform of relevant signals, one can obtain the formula for SSB signal modulated onto a carrier of frequency  $\omega_c$ :

$$E_{\text{SSB-mod}}(t) = E(t)\cos(\omega_c t) \pm \hat{E}(t)\sin(\omega_c t)$$

(3.2.6)

It is clear from Eq. s 3.2.4 and 3.2.6 that by applying a signal to one of the inputs of the optical IQ modulator, and its Hilbert transform to another input, it is possible to achieve single-sideband modulation in optical domain.

Optical IQ modulation is a mature technology [40] and is especially convenient when implemented in integrated optics [41–43], therefore enabling miniaturization and reduction in component cost.

## CHAPTER 3. INTRODUCTION TO CONTINUOUS VARIABLE QUANTUM KEY DISTRIBUTION

Figure 3.7: Hilbert transform amplitude and phase characteristics

Figure 3.8: Comparison between spectra of a baseband signal and their modulated variants

#### 3.2.4 Automatic bias controller

Controlling bias voltages in an IQ modulator is not a trivial task. In a regular IQ modulator there are three voltages to be kept under constant control in order to achieve optimal performance. The situation is complicated even more if dual polarization (DP-MZM) modulator is employed, where one needs to control six bias voltages. DP-MZM are two IQ modulators put in parallel using a polarizing beamsplitter in order to work with both polarization degrees of freedom. Automatic bias controllers (ABC) are used for fine tuning the bias voltages. The optical input provides the necessary feedback in order to maintain the DC bias voltage at the desired spot. This kind of ABC generally works well with any litium niobate (LiNbO3) optical modulator and at any data rates.

#### 3.2.5 Homodyne detection

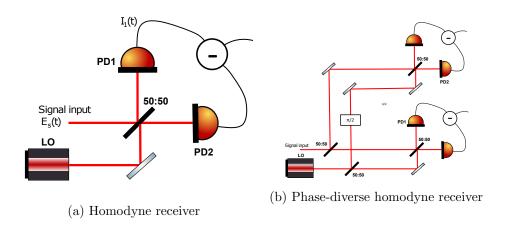

It was mentioned in Section 3.2.3, there was a period when both research and industry (in classical telecommunications) were focused on relatively simple and cheap direct detection schemes for optical communications. Physicists on the other hand, were interested in phase-sensitive measurements [46–49], as a complete description of a quantum state of light requires its associated phase information. For the purpose of having a phase-sensitive measurement, a coherent receiver configuration is employed. Coherent receivers use a reference coherent beam called the local oscillator (LO) in order to measure the complex amplitude of the receiving signal, as shown in Fig. 3.9. If the coupler used in the receiver is 50/50, the receiver is called the balanced

Figure 3.9: Optical coherent receivers

coherent receiver. Two output beams of the coupler are detected using a pair of photodiodes. In our work, this kind of device is called the *balanced homodyne receiver*, or just the *homodyne receiver*. Note that with the homodyne receiver, it is possible to perform a *homodyne*, *heterodyne* or a *phase-diverse homodyne* measurement. The difference between these terms is explained in the following paragraphs.

The derivation presented below can be found in [36]. Let  $E_s(t)$  be the input signal electric field (Fig. 3.9):

$$E_s(t) = \alpha_s(t)e^{i\omega_s t}, \qquad (3.2.7)$$

where  $\alpha_s(t)$  is the complex amplitude and  $\omega_s$  is the frequency of the signal laser. Similarly,  $E_{\rm LO}(t)$  is the local oscillator field with  $\alpha_{\rm LO}$  being the constant complex amplitude

$$E_{\rm LO}(t) = \alpha_{\rm LO} e^{i\omega_{\rm LO}t}.$$

(3.2.8)

Using the complex amplitudes, signal power of the both fields is calculated as

$$W_s = k|\alpha_s|^2/2,$$

(3.2.9)

$$W_{\rm LO} = k|\alpha_{\rm LO}|^2/2,$$

(3.2.10)

where  $k = S_{\text{eff}}/Z_0$ , and  $S_{\text{eff}}$  is the effective beam area and  $Z_0$  is the impedance of the free space.

The signal field and the LO filed are coupled at the balanced coupler (beam-splitter). Balanced detection is used in coherent receivers as a tool to suppress the DC component and maximize the beat between the signal and the

## CHAPTER 3. INTRODUCTION TO CONTINUOUS VARIABLE QUANTUM KEY DISTRIBUTION

LO [36]. Using the beamsplitter transformation covered in Section 3.2.2, the output fields are calculated as:

$$E_1 = \frac{1}{\sqrt{2}}(E_s + E_{LO}),$$

(3.2.11)

$$E_2 = \frac{1}{\sqrt{2}}(E_s - E_{\text{LO}}).$$

(3.2.12)

Now the photocurrents on the two photodiodes are calculated as

$$I_{1}(t) = k \frac{q_{e} \eta}{\hbar \omega_{s}} \left\langle \operatorname{Re} \left( \frac{\alpha_{s}(t) e^{i\omega_{s}t} + \alpha_{LO} e^{i\omega_{LO}t}}{\sqrt{2}} \right)^{2} \right\rangle$$

$$= \frac{q_{e} \eta}{2\hbar \omega_{s}} [W_{s}(t) + W_{LO} + 2\sqrt{W_{s}(t)W_{LO}} \cos(\omega_{IF}t + \theta_{s}(t) - \theta_{LO}(t))],$$

(3.2.13)

$$I_{2}(t) = k \frac{q_{e} \eta}{\hbar \omega_{s}} \left\langle \operatorname{Re} \left( \frac{\alpha_{s}(t) e^{i\omega_{s}t} - \alpha_{LO} e^{i\omega_{LO}t}}{\sqrt{2}} \right)^{2} \right\rangle$$

$$= \frac{q_{e} \eta}{2\hbar \omega_{s}} [W_{s}(t) + W_{LO} - 2\sqrt{W_{s}(t)W_{LO}} \cos(\omega_{IF}t + \theta_{s}(t) - \theta_{LO}(t))],$$

(3.2.14)

where  $\omega_{IF}$  is the difference between the signal and the LO frequencies  $\omega_{IF} = |\omega_s - \omega_{LO}|$ , and  $\theta_s(t)$  and  $\theta_{LO}(t)$  are the phases of the signal and the LO respectively.  $\eta$  is the quantum efficiency of the photodiode and  $q_e$  is the electron charge.

The output of the homodyne detector is the difference between the two currents:

$$I(t) = I_1(t) - I_2(t) = 2\frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t)W_{LO}} \cos(\omega_{IF}t + \theta_s(t) - \theta_{LO}(t)).$$

(3.2.15)

Eq. 3.2.15 shows that the output signal is proportional to the square root of the LO power. This means that by increasing the LO power, the amplitude of the received signal increases, and even for low input signals  $P_s$  there is a possibility of bringing the output signal level above the electronic noise of the detector. This is very important for measuring low level signals and intrinsic quantum noise, which is one of the central concepts in quantum optics. The detector which can bring the intrinsic quantum noise signal above the electronic noise is called the *shot noise limited* detector.

After getting the general expression for output current of the homodyne receiver, one can define different types of measurements. If the frequency of the LO is not the same as the frequency of the signal  $|\omega_{IF}| > 0$ , and

Figure 3.10: The in-phase component measured with the homodyne measurement

specifically if  $|\omega_{IF}| \gg B_s$ , where  $B_s$  is the measured signal bandwidth, this is a heterodyne measurement. In the literature, the case where  $|\omega_{IF}| \approx B_s$  is called intradyne scheme [50]. On the other hand, homodyne measurement is the one where there is the exact match between the frequencies  $|\omega_{IF}| = 0$ . In homodyne measurement the output current becomes

$$I(t) = 2\frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t) W_{LO}} \cos(\theta_s(t) - \theta_{LO}(t)).$$

(3.2.16)

If for now  $\theta_{LO}(t)$  is fixed to be constant and zero, since the time variation just represents the phase noise of the LO (LO phase is precisely controlled as it represents the reference), a simple expression is obtained that tells that the result of the homodyne measurement is nothing else but the in-phase component of the optical signal as shown in Fig. 3.10.

Homodyne measurement is not able to retrieve the full information about the complex amplitude. It is however possible to choose whether, during the symbol period, one wants to measure the in-phase or the quadrature component. This is done by fixing the LO phase for the in-phase measurement, and introducing LO phase shift by  $\pi/2$  when measuring the quadrature component. On the other hand, the heterodyne measurement is able to retrieve information about both quadratures:

$$I(t) = 2 \frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t) W_{\text{LO}}} \cos(\omega_{IF} t + \theta_s(t))$$

$$= 2 \frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t) W_{\text{LO}}} (\cos(\omega_{IF} t) \cos(\theta_s(t)) - \sin(\omega_{IF} t) \sin(\theta_s(t)))$$

$$\xrightarrow{\text{down+LPF}} \frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t) W_{\text{LO}}} \cos(\theta_s(t)) \quad \text{or} \quad \frac{q_e \eta}{\hbar \omega_s} \sqrt{W_s(t) W_{\text{LO}}} \sin(\theta_s(t)).$$

$$(3.2.17)$$

There is a third possibility when it is convenient to immediately get the baseband signal using a homodyne measurement, but also retreive the

information about both quadratures. This is called the *phase-diversity measurement* and it employs two homodyne detectors in parallel, couplers for the signal and the LO and a  $\pi/2$  phase shifter for the LO, as shown in Fig. 3.9b. The expression for the output currents is identical to the output of the heterodyne measurement, with a factor of 1/2, due to the additional 3 dB splitting.

In classical telecommunications, historically there were different reasons for using homodyning or heterodyning, such as the difficulty of having high intermediate frequency (IF) or optical phase locked loop (OPLL) [37]. In quantum communications there is another parameter of interest when deciding about the measurement scheme – the shot noise.

### Measurement of quantum states and shot noise

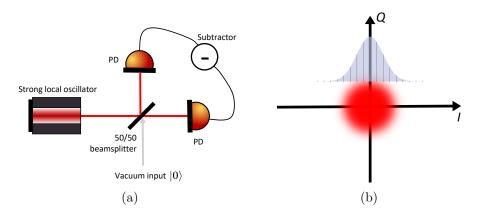

The intrinsic quantum uncertainty between the two quadratures of a light field is manifested in the inherent noise that is present in the absence of all other extrinsic noise. Homodyne measurement in a quantum setting is described in [51]. The setup is the same one as before shown in Fig. 3.9.

Fields are described now using field operators,  $\hat{E}_s(t)$  and  $\hat{E}_{\rm LO}(t)$  for the signal and the local oscillator respectively. The local oscillator is in a coherent state with a large power. It can be denoted by a ket vector  $|\sqrt{W_{\rm LO}/\hbar\omega_{\rm LO}}e^{-i\omega_{\rm LO}t}\rangle$ . LO power is much larger than the signal power  $W_{\rm LO}\gg W_s$ . Considering the homodyne measurement, where the signal carrier frequency and the LO frequency are equal, the detector output current operator is calculated as:

$$\hat{I}_{\text{hom}}(t) = 2q_e g \sqrt{\frac{\eta W_{\text{LO}}}{\hbar \omega_{\text{LO}}}} \int d\tau \operatorname{Re} \left( \hat{E}_s(\tau) \phi_{\text{LO}} e^{i\omega_{\text{LO}}\tau} \right) h_{\text{LP}}(t-\tau), \quad (3.2.18)$$

where  $q_e$  is the electron charge, g is preamplifier gain,  $\phi_{LO} = e^{i\theta_{LO}}$  is the phase of the local oscillator and  $h_{LP}$  is the impulse response of a low-pass filter. Previously shown, the homodyne detection measures the signal component that is in-phase with the LO phase  $\theta_{LO}$ .

For the heterodyne measurement, the same setup is used, however now the LO frequency differs from the signal carrier by  $\omega_{IF}$ . The state of the LO is  $|\sqrt{W_{\rm LO}/\hbar\omega_{\rm LO}}e^{-i(\omega_s-\omega_{IF})t}\rangle$ . Here, one needs to take care of the image band of the signal mirrored by the LO. The image band lies around  $\omega_s-2\omega_{IF}$  and the modes of this band are not active – they are in the vacuum state. Field operators associated with the signal and image band are  $\hat{E}_s(t)$  and  $\hat{E}_{\rm image}(t)$  respectfully. In semiclassical theory, the image band does not produce any current. This is not true in quantum theory for which the output current

operator can now be written as

$$\hat{I}_{\text{het}}(t) = 2q_e g \sqrt{\frac{\eta W_{\text{LO}}}{\hbar \omega_{\text{LO}}}} \operatorname{Re} \left( (\hat{E}_s(t) + \hat{E}_{\text{image}}(t)) \phi_{\text{LO}} e^{i(\omega_s - \omega_{IF})t} \right).$$

(3.2.19)

Here the band-pass filter impulse response is omitted for simplicity.

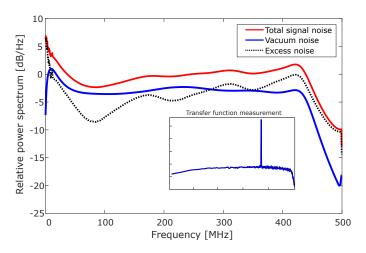

Eq. 3.2.18 shows that the noise obtained by measuring the output current does not come from the local oscillator, but from the measurement of the field operator  $\hat{E}_s$ . The signal can be in the vacuum state. Since this is also a coherent state, the homodyne measurement output will be the shot noise attributed to quantum uncertainty. The power spectral density of the shot noise is

$$S_{\text{shot}}(f) = \frac{g^2 \eta q_e^2 W_{\text{LO}}}{\hbar \omega_{\text{LO}}} |H_{LP}(f)|^2, \qquad (3.2.20)$$

where  $H_{LP}(f)$  is the frequency response of a low-pass filter that models the response of imperfect system. In CV-QKD and QRNG it is quite convenient take the shot noise level as a reference, as it is intrinsic and stays constant for constant LO power, quantum efficiency and detector gain. When this is the case, the power of the shot noise is called the *shot noise unit* (SNU).

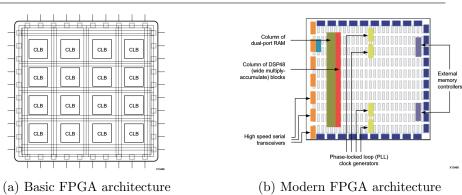

### 3.2.6 FPGA chips

This section provides an introduction to field programmable gate array (FPGA) chips and the motivations for their usage in quantum communications. It gives an overview of FPGA architecture, basic hardware primitives, and some designing techniques with FPGAs. There is a large set of textbooks and other literature about FPGAs and hardware design [52–55]. Note it is implicitly assumed Xilinx-made FPGAs are used, in particular Kintex UltraScale, that is used in this thesis. Appendix A provides detailed description of intellectual property (IP) cores used for our designs and other FPGA board related topics.

#### General FPGA architecture

There has been an ever increasing need in technological applications for more processing power and parallelization. Engineers can chose one of the several options when implementing a functionality or an algorithm. One option are single core microprocessors that can be very flexible and cheap, but may be too slow for some purposes. Another option are multi-core systems or graphical processing units (GPU) with thousands of cores, still very flexible, but more expensive and harder to program. On the other end of this spectrum are application-specific integrated circuits (ASIC), specialized pieces of hardware built only for one purpose. They are very fast, but expensive and not flexible. Somewhere in the middle of the processing device

Figure 3.11: Taken from [54](Xilinx)

spectrum lie FPGAs. It is a chip technology that addresses the cost and flexibility problem by implementing a large set of multipurpose and programmable primitives, but also keeping the high performance regarding the speed and latency compared to CPUs and GPUs. These facts makes FPGAs an optimal solution for a plethora of applications, especially in research and development.

FPGAs consist of hardware primitives. Bellow are listed hardware primitives of modern Xilinx chips. Not every design utilizes all of them, however they all have been an integral part of the firmware designs in this thesis.

• Every FPGA (even the simplest and cheapest ones) is composed of configurable logic blocks (CLB) and interconnections between them. There are also external inputs and outputs which are represented as wires on the edge of the chip in Fig. 3.11a [54]. CLBs contain the programmable logic for the FPGA and this basic logic was present in FPGAs from the birth of the technology. One of the primitives found in CLBs is four-input lookup table (LUT). LUT can implement any four-input Boolean function and is equivalent to a system of logic gates. It is basically a truth table where different combinations of the inputs yield different output values for different functions. The number of memory locations for N-input LUT is  $2^N$  and the total number of functions which can be implemented is  $2^{N^N}$ . CLBs also contain Multiplexers (MUXs) that are statically programmed. That means the data paths are defined upon FPGA programming. Furthermore, flip-flops are the basic storage units within the FPGA fabric. Flip-flops are always paired with LUTs so they assist in pipelining and data storage. Flip-flops incorporate data and clock inputs, clock enable input, reset and data output. The value from the data input is passed to the data output on every clock pulse. Clock enable pin is used for storing a value for more than one clock cycle.

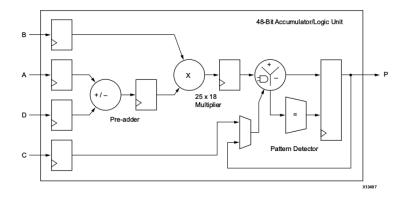

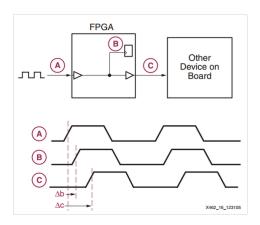

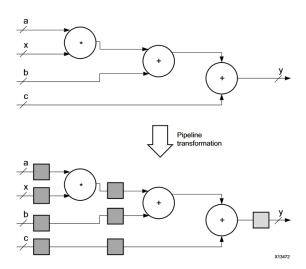

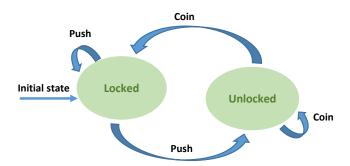

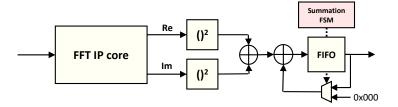

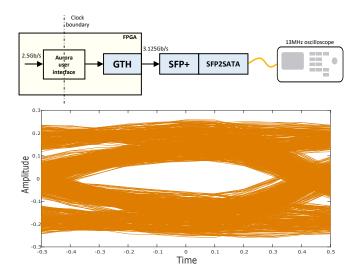

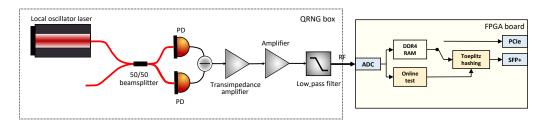

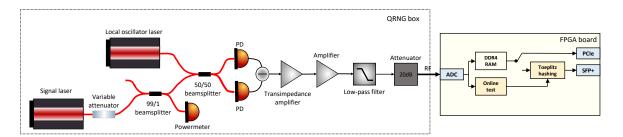

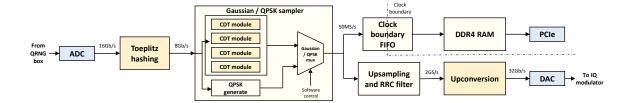

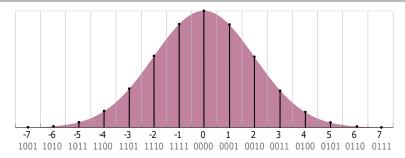

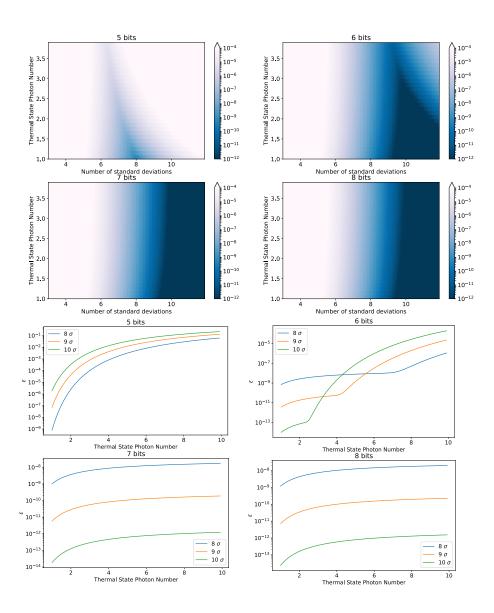

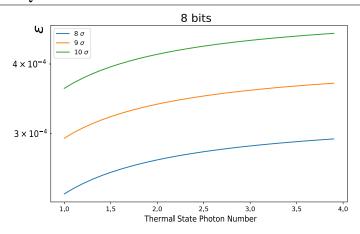

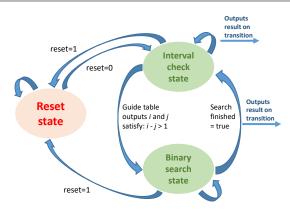

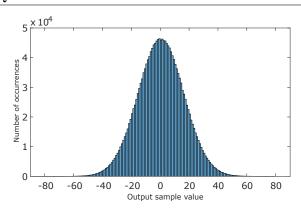

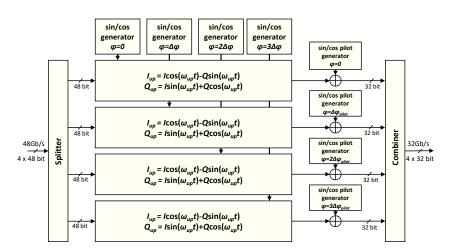

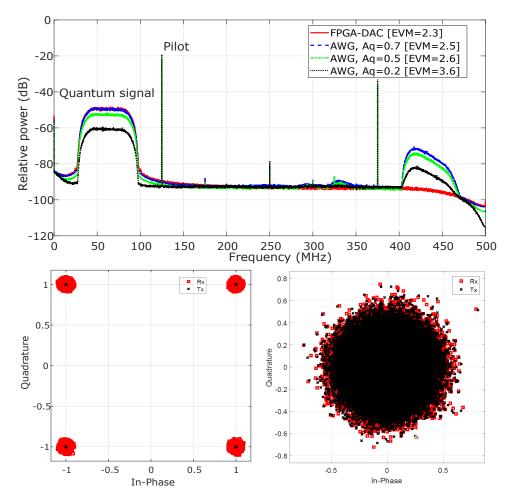

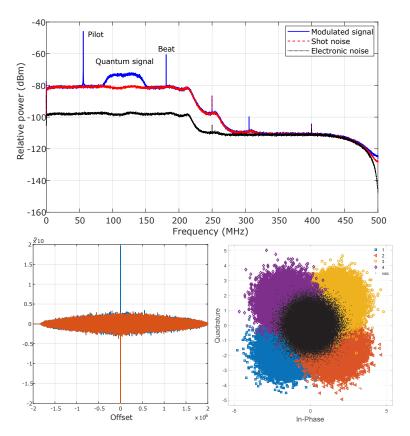

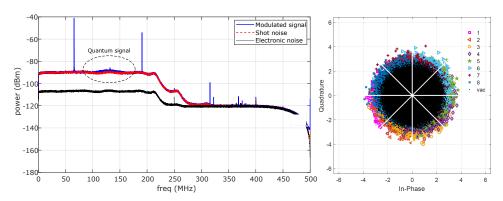

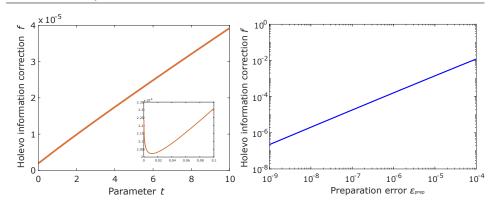

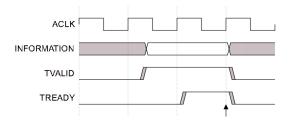

- Modern FPGAs contain, besides typical CLBs, several other specialized primitives that can sometimes drastically increase performance and platform flexibility. Fig. 3.11b shows the typical architecture of modern FPGAs. Standard CLBs are shown as grey rectangular boxes. For enabling high-rate multi-gigabit per second serial communications, modern FPGAs employ high speed serializer/deserializer (serdes) circuitries in high speed transceivers. The examples are GTX and GTH transceivers on Xilinx FPGAs.